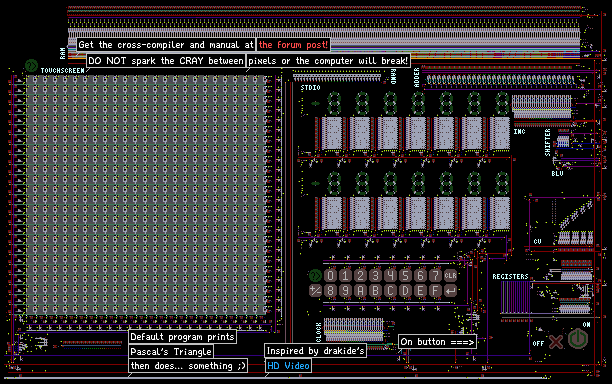

LightPC (0.6 Hz computer) by mark2222

A 0.6 Hz full-fledged WiFi-less 29-bit computer based on photon technology. Rather fast. WARNING: May lag. Note: The first part of the default program does not require input. Press the On button and LightPC will print Pascal's Triangle automatically.

light

filt

rllytouch

photon

screen

29bit

touchscreen

computer

processor

electronics

Comments

-

TheSpadesAce 13th Feb 2015

:O ! These electronic things are so cool! +1 for sure!

:O ! These electronic things are so cool! +1 for sure! -

ScienceNERD 16th Jan 2015

+1 dude

+1 dude -

Schmolendevice 31st Dec 2014

That is to say that the memory device will have 64 FILT particles, each storing 3 bytes, any of them being the start of a new instruction. So a CPU core is a single processing device with some RAM/ROM or instruction cache with an instruction cycle circuit, instruction register, program counter, decoder, internal bus and registers plus internal functional units that is capable of running a certain instruction set.

That is to say that the memory device will have 64 FILT particles, each storing 3 bytes, any of them being the start of a new instruction. So a CPU core is a single processing device with some RAM/ROM or instruction cache with an instruction cycle circuit, instruction register, program counter, decoder, internal bus and registers plus internal functional units that is capable of running a certain instruction set. -

Schmolendevice 31st Dec 2014

Yeah, in my case it's the opposite, not much experience with TPT computer hardware. Spent too much time 'not finishing' my real life project. TPT I money on electricity. MMU = memory management unit. Core is basically just a single parallel processor parallel to other cores which all run their own programs simultaneously. Well technically for now I'm planning to have an instruction set with arbitrary instruction width.

Yeah, in my case it's the opposite, not much experience with TPT computer hardware. Spent too much time 'not finishing' my real life project. TPT I money on electricity. MMU = memory management unit. Core is basically just a single parallel processor parallel to other cores which all run their own programs simultaneously. Well technically for now I'm planning to have an instruction set with arbitrary instruction width. -

mecha-man 31st Dec 2014

What is an MMU? By 24 bit do you mean up to a 24 bit number or 24 different instructions? What do you mean you can only fit 64 different ones? What do you define as a "CPU core". Sorry for all the questions I don't have much experience non-TPT computer hardware.

What is an MMU? By 24 bit do you mean up to a 24 bit number or 24 different instructions? What do you mean you can only fit 64 different ones? What do you define as a "CPU core". Sorry for all the questions I don't have much experience non-TPT computer hardware. -

Schmolendevice 29th Dec 2014

My plans are to have a coprocessor that manages program load requests for each core. So when one core is running, another core can ask the MMU to load a program or the next part of the program from memory and invoke an automated process.

My plans are to have a coprocessor that manages program load requests for each core. So when one core is running, another core can ask the MMU to load a program or the next part of the program from memory and invoke an automated process. -

Schmolendevice 29th Dec 2014

Ah, so repeatedly using certain console commands to send a bunch of PSTN to one location? Also, let's say if I had multiple mini CPU cores for a TPT computer, what would be a good size in terms of instructions for each core's L1 instruction cache? The design I'm working on will be able to fit 64 24 bit instructions. Should I ramp it up to 128?

Ah, so repeatedly using certain console commands to send a bunch of PSTN to one location? Also, let's say if I had multiple mini CPU cores for a TPT computer, what would be a good size in terms of instructions for each core's L1 instruction cache? The design I'm working on will be able to fit 64 24 bit instructions. Should I ramp it up to 128? -

mecha-man 29th Dec 2014

Well you can do that (sort of) right now using layering, I myself have used it extensively (and when the update comes out I will have to fix all my saves for it).

Well you can do that (sort of) right now using layering, I myself have used it extensively (and when the update comes out I will have to fix all my saves for it). -

Schmolendevice 29th Dec 2014

I just read online on the powder wiki what unofficially seemed to be the plan that PSTN will eventually be able to have the amount it extends and retracts set based on the number of increments by 10 C from 0 C in temp. Hence PSTN with a temp of 160 theoretically could push 16 FILT particles in a dense memory array but using only one or two PSTN particles.

I just read online on the powder wiki what unofficially seemed to be the plan that PSTN will eventually be able to have the amount it extends and retracts set based on the number of increments by 10 C from 0 C in temp. Hence PSTN with a temp of 160 theoretically could push 16 FILT particles in a dense memory array but using only one or two PSTN particles. -

mecha-man 29th Dec 2014

@Schmolendevice: What is going to be in there that can make it more compact?

@Schmolendevice: What is going to be in there that can make it more compact?